이번 연재는 초보 기술자나 신입사원들에게프린트 배선판 산업 및 기술 현황을 올바로 이해시키기 위해 기획되었다. 먼저 프린트 배선판의 산업 개요를 시작으로 그 종류와 기재, 프로세스, 제조 및 시험장치 등을 알아본다.

또 여기서는 프린트 배선판의 성능 및 특성, 원리, 구조, 종류, 응용 등을 도면과 함께 해설하였으므로 쉽게 이해할 수 있을 것이다.

전자산업에 있어서 기기는 점점 고성능화되고 있으며 경량, 소형화가 급속히 진행되고 있다. 이를 지원하고 있는 것이 전자

부품이다. LSI의 고집적화, 개별부품의 소형화 등과 같이 부품류는 급속히 진보하고 있다. 프린트 배선판은 전자기기 중에서 부품을 탑재, 접속하여 회로 모듈을 구성하는 데 중요한 역할을 담당하고 있으므로 진보된 프린트 배선판이 필요하다. 여기서는 고밀도, 고성능인 빌드업 프린트 배선판에 대한 개발배경, 제조 방법, 기타 사항에 관하여 개관한다.

프린트 배선판의 기능

프린트 배선판은 도체 배선과 그것을 지지하는 절연체로 구성되어 있다. 그 목적은 전자부품을 탑재, 접속하여 전자회로의 모듈을 형성함과 더불어 모든 전자부품을 지원하는 것이다. 프린트 배선판의 도입에 의해 부품의 접속법이 합리화되고 접속의 신뢰성 향상이 도모되었다. 현재는 소형₩휴대기기나 고성능 기기, 미소 모듈의 구성을 위해 고성능 프린트 배선판이 필요하게 됐고 미세 배선과 고다층화에 의한 단거리 배선, 고배선밀도가 실현되면서 고도의 전기 특성을 부여할 필요가 생겼다.

프린트 배선판의 재료로는 실리콘웨이퍼, 세라믹 기판, 유기수지기판이 있다. 이들은 각각 특징을 갖고 있어 적재적소에 사

용되고 있다. 유기 수지기판의 특징으로, 에너지 코스트가 낮아 양면에 접속할 수 있고 외형 형상을 자유롭게 가공할 수 있다는 점을 들 수 있다. 또한 베어칩 실장을 실행하는 패키지 기판의 영역에도 사용할 수 있게 되었다. 때문에 반도체 칩의 특성을 활용하는, 보다 고도의 기술이 요구되고 있다.

프린트 배선판도 전자부품의 하나이며 전기 특성은 중요한 부분이다. 도통저항, 절연저항 등의 기본적인 것뿐만 아니라 고주파신호를 충실하게 전송하기 위한 특성 임피던스 정합의 고정밀도화도 중요하다.

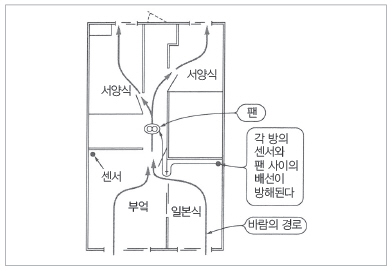

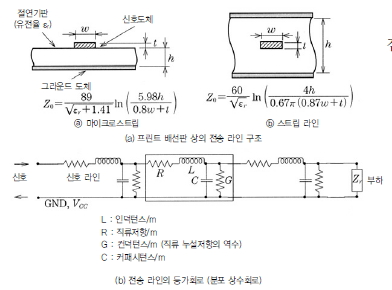

▲ 그림 1. 고주파 신호의 전송 라인 구조

전자기기의 구성과 배선밀도

프린트 배선판이 없는 전자기기는 존재할 수 없다. 전자기기는 LSI나 많은 전자부품을 프린트 배선판 상에서 계층구조로,

또 순서대로 접속하여 크고 작은 전자기기를 이루고 있으며 LSI에 내장된 기능을 가급적 활용할 수 있도록 연구되고 있다.

ITRS2004 로드맵의 High performance에 대해 2005년과 2010년을비교하면1) Technology mode :‘ 90 →45nm’, Logic

LSI의Tr 집적도:‘ 97 →309M trs/cm2’, 칩내클록주파수:‘5.1GHz →12.0GHz’, 칩to 보드:‘ 3.9GHz →7.6GHz’로 되어 있다. 칩 사이즈는‘310mm2로 불변’이고 I/O 핀 최대 : ‘3,400 → 4,009 핀’으로 됨으로써 I/O 핀의 피치가 미세해지고 칩을 실장하는 프린트 배선판도 미세하게 된다.

LSI 칩 내의 배선에 있어서 베이스의 기능소자 접속은 나노 레벨이지만, 칩 내부 배선의 십 수층을 거쳐 I/O 핀에 이르는

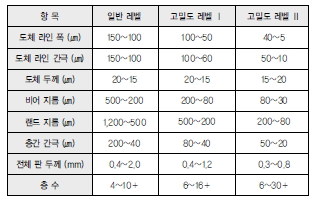

접속 패드 부근에서는 1∼5㎛로 된다. 프린트 배선판의 팬 아웃을 고려하여 10∼5㎛ 정도로 밸런스가 맞춰져 있으며, 가까운 미래에 배선 폭 10㎛가 실용화되고 폭 5㎛도 실현 가능성이 있다고 생각된다. 프린트 배선판의 배선 룰은 표 1과 같이 생각 할 수 있다.2)

▲ 표 1. 프린트 배선판의 배선 룰

프린트 배선판에 필요한 전기 특성

주요 전기 특성으로 다음과 같은 항목을 들 수 있다.3) 도체저항, 절연저항, 특성 임피던스(Z0)의 정합, 신호전파속도(υ), 유전체 손실, 반사계수(G), 표피효과, 인덕턴스, EMI 대책 등으로, 이들 중 주요 사항에 관하여 살펴본다.

1. 직류저항

도체 패턴은 급속하게 미세화하고 있다. 동도체의 패턴 길이가 50mm일 때, 전기저항값을 34.8Ω, 5.8Ω으로 하면 그 도체 단

면적은 25㎛2, 150㎛2로 된다. 그 때의 도체 폭과 두께는,

· 도체 단면적 25㎛2 : [폭 30㎛, 두께 0.85㎛], [폭 20㎛, 두께 1.25㎛], [폭 10㎛, 두께 2.5㎛]

· 도체 단면적 150㎛2 : [폭 30㎛, 두께 5.0㎛].[폭 20㎛, 두께 7.5㎛], [폭 10㎛, 두께 15㎛]

로 된다. 회로설계에서 저항의 허용값은 다르지만 작은 것이 요구되어 파인화되면 도체 두께가 커진다.

그 외에도 파인화에 의해 도체의 기계적 강도, 절연기판과의 접착력에 대한 대책이 필요하다.

2. 절연저항

고밀도 도체 배선에서는 절연간격도 미세해지므로 절연저항을 높은 값으로 해야 한다. 그러나 유기수지에서는 그 구성이 복잡하고 필요한 특성을 내기 위해 그 조성의 최적화가 필요하며, 특히 불순물 조정이 필요하다. 또 도체간 절연은 수지 자체나 계면에 따라 열화되는 경우도 많다. 절연의 신뢰성을 높게 유지하는 것이 앞으로 점점 중요해질 것이다.

3. 특성 임피던스(Z0)의 정합

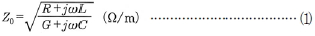

특성 임피던스는 식 (1)과 같이 나타낸다.

프린트 배선판에 있어서 전송 라인의 도체는 그림 1(a)와 같이 마이크로스트립과 스트립 라인이 있다. 또 전송 라인은 그림 1(b)와 같이 분포상수로 표현된다. Z0은 도체 폭과 두께, 그라운드와의 거리, 그 사이 절연체의 비유전율로 결정된다. 실제의 값은 그림에 있는 실험식 등에 의해 계산된다.

특성 임피던스는 설계에 의해 지정되고 그 정합이 엄격하게 요구되며 신호 라인의 폭이나 층간거리의 정밀도가 엄격하므로

제조기술의 향상이 필요한 부분이다.

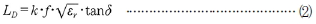

4. 유전체 손실의 감소

신호가 전파될 때, 신호는 그 동안 감쇠한다. 전체 감쇠(LT)는 도체 손실(LC)과 유전체 손실(LD)과의 합이다. 주파수가 커지면 신호의 감쇠에서는 유전체 손실(LD)이 커지고 식 (2)의 tanδ에 크게 의존하므로 이 값이 작은 재료가 요구되고 있다.

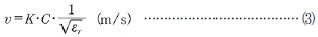

5. 신호 전파속도의 고속화

도체를 전송하는 신호의 속도(υ)는, 그 주위의 절연체 비유전율(εr)과 식 (3)과 같은 관계이다.

절연재료로서 저유전율재의 개발이 각 방면에서 진행되고 있다. 그러나 회로설계의 진전도 크고 통상적인 재료로도 상당한

고주파 대응이 가능해지고 있으므로 5GHz 이상의 고주파에 대응할 때 필요할 것이라 생각된다.

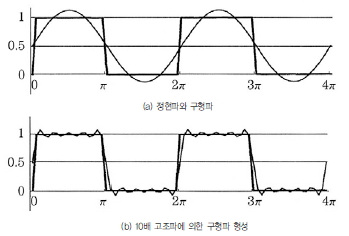

신호는 구형파로 전송하지만 구형파는 정현파에 분해된다. 그림 2와 같이 기본 정현파에 10배까지의 고조파가 합쳐짐으로써거의 구형파에 가까워진다. 따라서 프린트 배선판 상의 클록 주파수가 커질 경우, 실제로는 그 값의 10배에 가까운 정현파를 충실하게 전송시켜야 하므로 이 영역에서 저유전율재가 필요할 것이라 상정할 수 있다.

▲ 그림 2. 정현파와 구형파

6. 표피효과

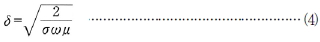

신호의 주파수가 커지면 전송하는 신호는 도체의 표면에 가까운 곳으로 집중된다. 이것을 표피효과라고 한다. 도체의 전도도는 내부로 갈수록 작아지며 그 값이 1/e로 되는 곳을 표피 두께(Skin depth, δ)라 하여 식 (4)와 같이 나타낸다.

이 표피효과에 의한 두께를 표 2에 나타낸다. 이 표에서 GHz대가 되면 표피효과가 현저해진다. 때문에 도체 표면의 형상이전송하는 신호에 영향을 미치게 되고 평활한 도체표면이 필요해진다. 지금은 개발 단계이지만 제조기술이 크게 관계하여 개발되고 있다.

▲ 표 2. 표피효과의 두께

빌드업 다층 프린트 배선판의 프로세스

1. 도체 배선 접속의 작성 프로세스와 그 재료

면 방향의 도체 배선은 동박이나 동 도금층의 에칭, 도금 레지스트를 이용한 패턴 도금법으로 작성된다. 판 두께 방향(Z 방향)의 접속은 구멍 안의 도금 또는 구멍 안으로의 도전성 페이스트충전에 의해 실행되고, 프린트 배선판의 프로세스는 표면의 도체 패턴 작성과 Z 방향 접속의 작성이 조합된 프로세스로서, 이용하는 방법에 따라 면 방향 패턴 정밀도에 영향을 미친다.4)

최근에는 빌드업 프린트 배선판 프로세스가 클로즈업되고 있다. Z 방향의 접속에는 도금법, 도전성 페이스트법, 땜납 도금법등이 있다. 기본 도금법은 기존의 도금 스루홀 프로세스이다. 빌드업 프로세스는 도금법, 도전성 페이스트법 모두 절연재료와밀접하게 관계되어 있다.

2. 도금을 이용한 빌드업 프로세스

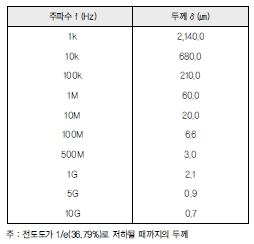

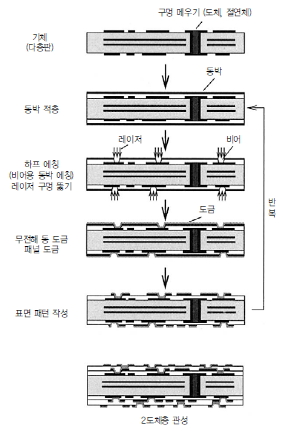

그림 3에 도금법에 의한 각종 빌드업 프로세스를 비교했다.5)

이 그림은 빌드업층의 1층을 형성하는 과정을 나타내고 있고 재료와 구멍 뚫기법 및 도금법에 따라 분류하고 있다. 재료는 수지장착 동박(수지 코트 동박, RCC) 동박/프리프레그법, 열경화성수지 및 감광성 절연수지의 3종류이다.

▲ 그림 3. 도금법에 의한 빌드업 프로세스

빌드업 프린트 배선판은 코어 기판상에 빌드업층으로서의 절연층과 도체 패턴을 형성한 것이다. 코어 기판은 이미 패턴이 형성된 프린트 배선판이고 스루홀에는 수지로 충전한 것이 있다.

수지층의 접착을 향상시키는 적층 전처리는 기존의 도금 스루홀다층 프린트 배선판의 프로세스와 같다. 빌드업 프로세스에서는 휨·뒤틀림을 방지하기 위해 코어 기판 양면에 대칭이 되도록 빌드업층을 형성한다.

(1) 수지 장착 동박재료의 프로세스

가장 광범위하게 사용되고 있는 방법이다.6) 이 재료를 적층 프레스로 코어 기판 또는 1층 형성한 빌드업층 상에 접착 성형한다. 동박/프리프레그를 이용하는 경우에는 기존과 마찬가지로적층편성, 가열 가압에 의해 프레스 성형을 실행한다. 여기서 이용하는 동박은 2∼3㎛로 얇을수록 좋지만, 처리 부분에서 두께12㎛인 것이 많다. 그 후, 필요에 따라 하프에칭에 의해 2∼3㎛로 하는 방법도 시행되고 있다. 동박을 이용하므로 수지와 도체의 접착성은 양호하다.

구멍 뚫기는 CO2 레이저를 이용하는 경우가 많지만 50㎛ 이하의 미세한 구멍을 뚫는 경우에는 UV-YAG 레이저를 이용하

고 있다. 레이저의 마스크로서 동박의 에칭에 의해 컨포멀 마스크로 하는 경우가 있지만, 최근에는 레이저의 성능이 향상되어조건 조정에 의해 동박을 직접 가공, 구멍을 뚫고 있다.

동박/프리프레그에 구멍을 뚫는 경우 동박, 수지, 유리섬유를동시에 가공하므로 구멍 뚫기 조건 조정에는 충분한 주의가 필요하다. 균일한 구멍 뚫기가 가능하도록 섬유를 균일하게 분포시킨 유리 직포도 개발되어 있다.

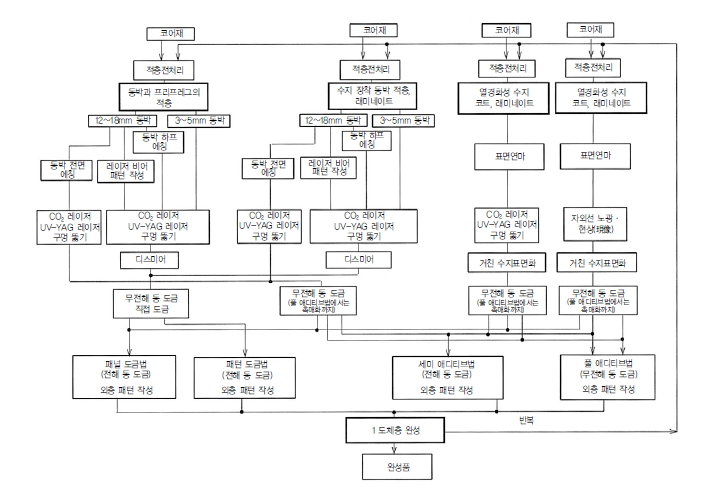

레이저로 구멍을 뚫은 후, 디스미어의 공정을 거쳐 도금을 실행한다. 도금법은 서브트랙티브법과 애디티브법이 있다. 이것은패턴 작성과 관계가 있어 후술한다. 수지장착 동박과 동박/프리프레그법은 동박을 가진 서브트랙티브법의 2가지 방법에서 선택된다. 현재는 대부분의 경우 패널 도금법이다. 도금 후, 표면패턴을 에칭 형성하여 1도체층이 완성된다. 이것을 반복함으로써 빌드업층을 겹칠 수 있다. 이 프로세스를 그림 4에 나타낸다.

▲ 그림 4. 수지 장착 동박을 이용한 빌드업 프로세스

(동박 마스크 레이저 비어/패널 도금법)

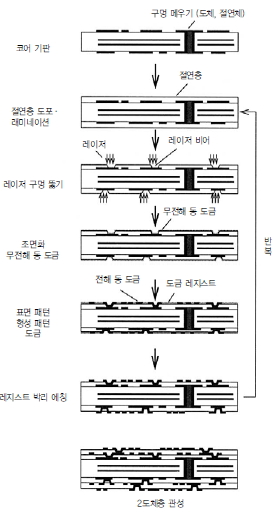

(2) 열경화성 수지재료의 프로세스

열경화성 수지를 사용하는 경우, 적층 전처리 후 액상의 수지를 코팅하거나 필름상의 것을 래미네이트한다, CO2 레이저 또는YAG 레이저로 구멍을 뚫는다. 무전해 동 도금과 수지의 접착성을 높이기 위해 수지표면을 거칠게 한 후 도금, 외층형성을 실행한다. 도금법은 세미 애디티브법을 이용하고 있다. 그림 5에 이재료가 이용된 프로세스를 나타낸다.

▲ 그림 5. 열경화성 수지·세미 애디티브법에 의한 빌드업 프로세스

(3) 감광성 절연수지재료의 프로세스

감광성 절연수지를 이용하는 경우, 마스크를 사용하여 자외선으로 노광, 현상하여 구멍을 뚫을 수 있다. 그 후의 프로세스는열경화성 수지와 같다. 감광성 절연재료에는 다양한 문제가 있어 현재는 개발되지 않으며 적용되는 경우도 거의 없어졌다.

3. 도전성 페이스트를 이용하는 빌드업 프로세스

Z 방향을 도전성 페이스트에 의해 접속하는 빌드업법으로 현재 2종류가 개발되고 있다.

(1) ALIVH법

액정 폴리머포 또는 유리직포를 이용한 프리프레그에 레이저로 구멍을 뚫고 여기에 도전성 페이스트를 충전, 동박과 적층 접착하여 일체화한다. 이 표면을 포토에칭법으로 패턴 작성하면양면판이 된다. 이 양면에 도전성 페이스트를 충전한 프리프레그와 동박을 적층하고 표면 패턴을 형성하면 4층판이 된다. 이와같이 순차적으로 접속하여 다층화하는 방법이다.

(2) B2it법

이 방법은 동박 또는 절연기판 상에 도전성 페이스트 추를 인쇄로 형성하고 프리프레그를 기계적으로 관통시켜 동박과 적층접착시킴으로써 Z 방향 접속을 실행하는 것이다. 표면의 도체패턴은 포토에칭법에 의해 형성한다. 도전성 페이스트 추의 작성, 동박과의 접착을 반복함으로써 다층화를 실행하고 있다.

도전성 페이스트법에 의한 표면 패턴은 대부분의 경우, 동박의 에칭으로 작성되므로 도체 두께가 큰 파인 패턴을 실현하는

데에는 한도가 있다고 생각된다.

프린트 배선판의 제조기술에 관한 최근 개발동향

다층 프린트 배선판에서는 다양한 프로세스가 제안되어 실용화되고 있는데, 부가가치를 높이기 위해 파인화를 추진하여 전

기 특성을 향상시키기 위한 기술개발이 진행되고 있다. 이들 몇가지를 소개한다.

1. 서브트랙티브법과 애디티브법

도금 스루홀법에서는 구멍 내의 도통화와 표면 패턴 형성을동시에 실행하고 있다. 파인 패턴이 요구되고 있으므로 표면의

도체 패턴 형성과 비어의 접속 도금과의 관계가 중요해진다. 도금법으로 작성하는 데에는 서브트랙티브법과 애디티브법이 있으며 각각 특징을 갖고 있다. 파인화의 가능성을 중심으로 이 방법들을 비교한다.

서브트랙티브법은 절연체 수지표면에 미리 동박이 있는 절연기판을 출발 물질로 한다. 애디티브법은 절연체 수지표면을 직접 도통화하는 것으로, 도통화법을 무전해 동 도금에 의한 것으로 했다. 서브트랙티브법에는 전면에 도금하는‘패널 도금법’과패턴부에만 도금하는‘패턴 도금법’이 있다. 애디티브법에는 무전해 동 도금으로 도통화한 후에 패턴 부분을 전해 동 도금으로작성하는‘세미 애디티브법’과, 무전해 동 도금만으로 작성하는‘풀 애디티브법’이 있다. 애디티브법에도 전면에 도금하는 패녈법이 있지만 여기서는 생략한다.

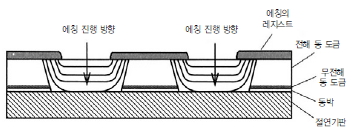

(1) 패널 도금법

무전해 동 도금 후, 그림 6과 같이 패널 전면에 전해 동 도금을 실행하는 방법이다. 수지 장착 동박재료, 동박/프리프레그 재료를 이용하는 빌드업 프로세스에 많이 이용되고 있다. 패널 도금 후, 포토에칭법에 의해 에칭 레지스트로 표면 패턴을 에칭하고 도체 패턴을 작성한다. 이 때의 에칭량은 동박 두께와 도금두께의 합계가 된다.

에칭 레지스트는 표면에 있고 에칭의 진행 방향은 등방성이며사이드 에칭에 의해 패턴 폭의 정밀도 변동이 크므로 파인 패턴작성에는 한도가 있다. 비어의 구멍 내 도금은 패턴 에칭 전에보호할 필요가 있으므로 레지스트에 의한 텐팅 혹은 플러깅에의해 보호하고 있다. 이 방법은 동박이 있으므로 무전해 동 도금으로 교체, 다이렉트 플레이팅의 프로세스를 이용할 수 있다.

▲ 그림 6. 패널 도금법

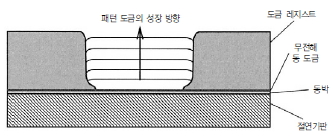

(2) 패턴 도금법과 세미 애디티브법

패턴 도금법은 동박을 가진 재료인 수지 장착 동박재료, 동박/프리프레그 재료를 이용한 것에 적용된다. 구멍 뚫기, 무전해 동도금 후, 그림 7과 같이 도금 레지스트에 의한 도금 패턴을 작성,전해 동 도금을 실행함으로써 도체 패턴을 형성하는 방법이다.

▲ 그림 7. 패턴 도금법

서브트랙티브법은 패널 표면이 수지뿐인 것에 적용되며 구멍뚫기, 무전해 동 도금 후, 전해 동 도금에 의해 패턴 도금을 실행하는 방법이고 이 양자는 동박의 유무에 따라 다르므로 프로세스에는 큰 차이가 없다. 어느 것이든 패턴 폭은 레지스트의 해상도로 결정되지만 동박이 있는 패턴 도금법에서는 표면에 동박이있으므로 무전해 동 도금의 두께가 가해져 에칭의 양이 많아지므로 패턴 정밀도가 저하된다.

따라서 동박을 얇게 하는 하프 에칭법이나 2∼3㎛ 두께의 극박 동박을 적용하여 정밀도를 높이고 있다.

열경화성 절연수지를 이용했을 경우, 표면에 동박이 없어 세미 애디티브법이 적용되고 있다. 패턴 도금 후의 에칭은 무전해

동 도금층뿐이므로 고정밀도의 패턴을 작성할 수 있다. 그림 7에서 동박이 없는 것에 해당한다. 미세 배선으로 도체 높이가 큰도체로할수있는세미애디티브법이 주목받고 있다.7)

여기서 주의해야 할 점은, 무전해 동 도금은 전해 동 도금보다에칭 속도가 빨라 언더 컷으로 된다는 점이다. 미세 배선일 경우큰 문제가 되므로 무전해 동 도금의 조성, 조건 및 에칭액이나조건의 검토가 필요하다. 동 도금 후 에칭 레지스트로서 땜납이나 주석의 도금을 실행하는 경우가 있다.

밀착성에 관해 동박이 있는 패턴 도금법에서 수지와의 밀착성은, 지금까지의 동장적층판과 같이 처리함으로써 접착성을 크게할 수 있다. 그러나 수지 표면 위를 도통화하는 세미 애디티브법에서는 현재, 수지를 거칠게 하고 앵커 효과에 의해 밀착성을 내게 되므로 특수한 수지조성과 처리가 필요하다. 그러나 무전해동 도금/수지계면은 전기특성 상 평탄한 것이 바람직하다.

패턴 도금/세미 애디티브법에서는 패턴의 조밀(粗密)함에 따라 전해 동 도금의 두께 분포가 커지고 세미 애디티브법에서는

도체간 절연부분에 잔류하는 Pd 촉매의 제거가 필요하다는 등의 문제가 있다.

지금까지 세미 애디티브법에 의해 10㎛ 도체 폭의 프린트 배선판을 얻었으며 5㎛를 실현할 가능성을 갖고 있다.

(3) 풀 애디티브법

이 방법은 수지 표면을 Pd로 촉매화하고 내알칼리성이 있는도금 레지스트로 패턴을 형성한 후, 무전해 동 도금에 의해 도체패턴을 작성한 것이다. 이것은 무전해 동 도금 석출 시간이 길고물성의 컨트롤이 어렵다. 또한 무전해 동 도금 관리, 내알칼리성도금 레지스트 등 특수한 것이 필요하다는 등의 이유로 현재는보급되지 않고 있다.

2. 필드 비어와 스택 비어

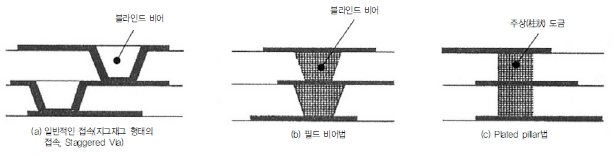

빌드업 프린트 배선판에 있어서 컨포멀 비어는 일반적이다.

이 컨포멀 비어에서는 다중층 사이를 접속할 경우, 그림 8(a)와같이 지그재그 형태로 접속된다.8)

그림 8(b), 그림 8(c)는 비어를 바로 위에 접속하는 방법의 스택 비어를 나타낸다.

▲ 그림 8. 다중층 접속 방법

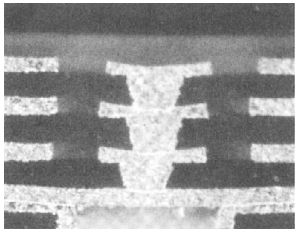

도금 이외에 도전성 페이스트 등의 도체를충전한 것도 있다. 스택 비어에서 접속하면 지그재그 형태의 접속보다 인덕턴스가 절반 이하로 되어 전기 특성을 향상시키는동시에 효율적으로 배선할 수 있다. 스택 비어의 예를 사진 1에나타낸다.

▲ 사진 1. 필드 비어의 예 (50㎛ 지름, 3단 스택)

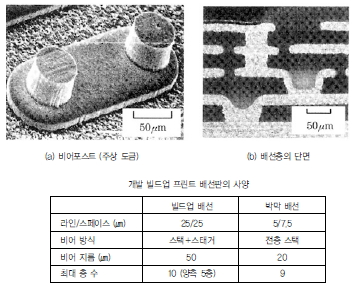

이 비어의 안을 동 도금으로 충전하는 필드 비어 개발이 성행하고 있으며 일부에서는 실용화되고 있다. 이 방식은 구멍 안과표면의 도금 전류를 첨가제에 의해 제어하는 것으로, 표면에 전류를 억제하는 첨가제, 구멍 내부에 전류를 촉진하는 첨가제를흡착시킴으로써 달성한다. 계속되는 연구에 의해 급속히 개선되고 있지만 장기간에 걸쳐 안정적으로 가동시키기 위해서는 더많이 검토돼야 한다. 또 도금의 물성이나 세미 애디티브법에의적용 등에 관해서도 향후 개발이 필요하다고 생각된다. 스택 비어를 실현하기 위해 비어 구멍 뚫기에 레이저 등을 이용하지만 이것을 이용하지 않는 방법도 있다. 그림 9와 같이 열경화성 절연수지를 사용하여 패턴과 함께 주상 도금(범프 도금)을 형성하고 순차적으로 접속하는 빌드업법이다.9)

▲ 그림 9. 주상 도금에 의한 빌드업 프로세스

이 방식은 세미 애디티브법에 의한 것으로, 그림 10의 예와 같이 미세한 비어를 형성하고 있다.10) 이 범프를 에칭으로 형성하는 방법도 있다. 또 전사법의 적용 등도 고려되고 있으며11) 보다 미소한 지름의 비어 형성에 대해 개발이 진행되고 있다.

▲ 그림 10. 주상 도금에 의한 비어 형성

3. 평활면의 접착 방법

현재 수지와 금속의 접착면은 금속을 조면화(粗面化)하고 앵커 효과로 인장 강도(필 강도)를 크게 하고 있다. 그러나 고주파가 될 경우 신호는 표면을 흐르므로, 전기 특성을 향상시키려면금속의 접착면은 평활한 것이 필요하다. 그러나 이 접착 방법은현재 개발 중에 있다.

금속과 수지의 접착에는 수지가 유동하여 금속면에 접착하는케이스와 수지면에 무전해 도금의 금속을 접착시키는 케이스가있다.

전자에는 평활 동박에 특수한 접착처리재를 적용하고 접착조건을 최적화함으로써 효과를 높이고 있다. 후자에 관해서는 곤

란한 부분이 있지만, 산화 티탄분을 물에 현탁시킨 액으로 패널을 침지하여 자외선을 조사하는 방법이 있다.12) 조사에 의해 수지가 개질되고 나노 오더의 미세한 구멍이 가능해짐에 따라 Pd의접촉입자가 고착되고 밀착성이 좋은 무전해 동 도금이 가능하게된다고 보고되고 있다.

빌드업 프린트 배선판의 신뢰성

전자기기 중 전자부품을 지원하는 프린트 배선판의 신뢰성은 중요한 부분이다. 와관검사, 전기검사에서 발견되지 않는 프린트 배선판 내부의 수지 스미어, 구멍 내부의 도금 크랙, 미세한박리에 의한 절연열화 등 잠재되어 있는 결함에 기인하는 경우가 많다. 이들이 필드에 나와 나타나면 기기의 신뢰성에 크게 영향을 미친다.

특히 파인화된 도체 패턴에서는 절연기판의 열팽창에 의한 신축으로 배선의 단선이 염려되고, 또 절연간극이 미세해지므로

도체간 절연은 매우 중요하다. 때문에 열충격 시험이나 가습열화 시험을 실행하여 평가하는 동시에 도체재료의 물성, 접착성혹은 절연재료의 절연성 향상이 도모되고 있다.

특히 절연에 있어서 가습열화 시험의 조건은 85℃/85% RH의조건이 표준이지만 결함이 나타날 때까지 시간이 걸리므로 단시간에 결과를 내기 위해 비정상적인 시험인 PCT, HAST 등이 요구되고 있다. 그러나 재료의 특성을 무시한 조건이 부과되는 경우도 있어 현실과 괴리될 우려가 있다. 이러한 시험에 관해 보고된 것도 있지만13) , 앞으로는 적정한 시험법의 개발이 요구되는 실정이다.

프린트 배선판의 전망

지금까지 진행되어온, 파인 패턴을 가진 고밀도· 다층 프린트 배선판, 극박형의 다층 프린트 배선판, 플렉스 리지드 다층 프린트 배선판 등, 혹은 특성 임피던스 제어 프린트 배선판 등 더욱고도의 것으로 개발이 진행되고 있지만 이들을 실용화하는 데에는 빌드업 프로세스가 매우 효과적이다.

또한 베어 칩 탑재 패키지인 BGA, CSP나 System in Package(SiP, MCM) 기판, 부품 내장 프린트 배선판 등을 유기수지

계의 절연재료로 실현하는 데에는 이 빌드업 프로세스가 핵심을이룰 것이라 생각된다.

本記事는 日本工業調査會가 發行하는「電子材料」誌와의 著作權協定에 依據하여 提供받은 資料입니다.

게재월 | 2006 - 06  1430

1430  0

0