3.2 X 1.6mm에서 100㎌!

적층 세라믹 콘덴서의 특징과 사용 방법

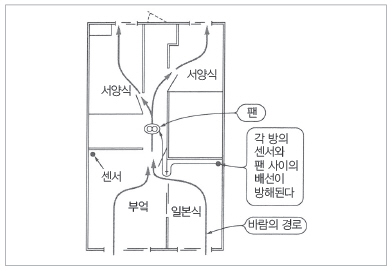

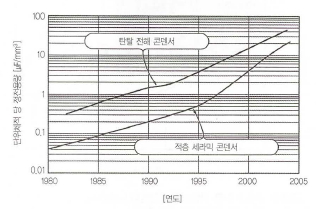

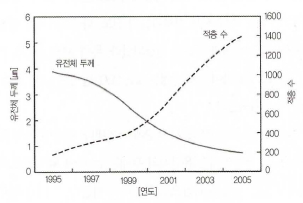

최근 적층 세라믹 콘덴서의 정전용량은 빠른 속도로 증대되었으며 특히 1990년대 후반부터의 소형 대용량화 흐름은 무어의 법칙(미국 인텔사 창설자 중 한사람인 고돈 무어 씨가 1965년에 제창한 법칙. 반도체의 집적밀도는 18~24개월에 2배로 된다는 것. 반도체업계에서는 유명한 법칙)에 필적할 정도의 하이 페이스이다.

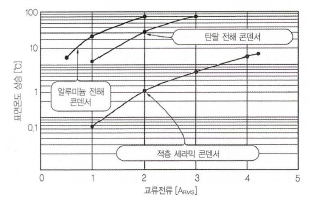

1980년대에는 단위 체적 당 정전용량이 탄탈 전해 콘덴서의 약 1/10이었지만 2000년에는 100㎌의 대용량 제품을 양산할 수 있게 되어 그림 1과 같이 적층 세라믹 콘덴서의 정전용량 체적비는 탄탈 전해 콘덴서의 약 1/2까지 압축되고 있다.

▲ 그림 1. 적층 세라믹 콘덴서와 탄탈 전해 콘덴서의 정전용량 체적비

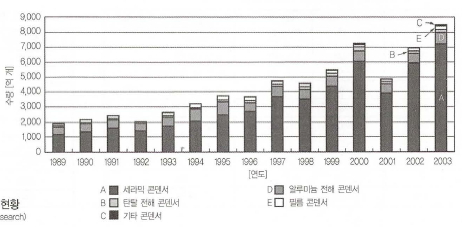

이 흐름과 함께 적층 세라믹 콘덴서는 모든 전자기기에 탑재되고 있다고 해도 과언이 아닐 정도로 보급되어 왔다. 그리고 생산수량에 있어서는 그림 2와 같이 전자기기용 콘덴서 전체의 80% 이상을 차지하는 데 이르고 있다.(1)

▲ 그림 2. 세계 전자기기요 콘덴서의 생산 현황

(World Capacitor Report/EIA Market Research)

이러한 시장확대는 적층 세라믹 콘덴서의 전기적 특성, 신뢰성이 우수함이 시장에서 인정된 결과이며 앞으로 더욱 활발한 확대가 기대되고 있다.

적층 세라믹 콘덴서는 전해 콘덴서 등과는 다른 전기적 특성을 나타내므로 성능을 100% 활용하기 위해서는 그 특징을 잘 이해한 다음에 사용해야 한다.

여기서는 적층 세라믹 콘덴서의 장점을 최대한으로 발휘하기 위한 전기적 특징과 취급 방법에 관하여 해설한다.

종류와 특징

1. 적층 세라믹 콘덴서와 기타 콘덴서의 분포

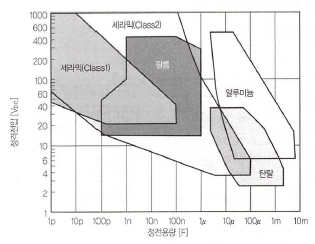

현재 전자기기에서 주로 사용되고 있는 콘덴서에는 적층 세라믹 콘덴서 외에 탄탈 전해 콘덴서, 알루미늄 전해 콘덴서, 필름 콘덴서 등이 있다.

세라믹 콘덴서는 크게 단판형과 적층형으로 나뉘지만 오늘날에는 90% 이상이 적층형으로 되어 있다. 각종 콘덴서의 취득용량범위를 그림 3에 나타낸다.

▲ 그림 3. 종류별로 본 콘덴서의 용량범위 (칩 타입에서 100㎌이라는 대용량 적층 세라믹 콘덴서가 이미 시판되고 있다)

적층 세라믹 콘덴서는 소형 대응, 고내압, 다양한 온도 특성 등 많은 품종이 갖춰져 있으며 미소용량에서부터 대용량까지 폭넓은 취득용량범위를 갖고 있다. 그리고 Class2 콘데서의 100㎌을 훨씬 상회하는 대용량화, Class1 콘덴서의 고용량화 등에 의한 대전류의 파워 애플리케이션 용도로의 시장확대도 기대되는 바이다.

알루미늄 전해 콘덴서나 탄탈 전해 콘덴서는 대용량이라는 장점을 갖고 있다. 주로 10㎌을 초과하는 용량 영역에서 사용되어 더욱 소형화, 대용량화 대책이 이루어지고 있다.

최근에는 특히 도전성 고분자 재료를 음극에 사용한 전해 콘덴서가 등장하고 있다.

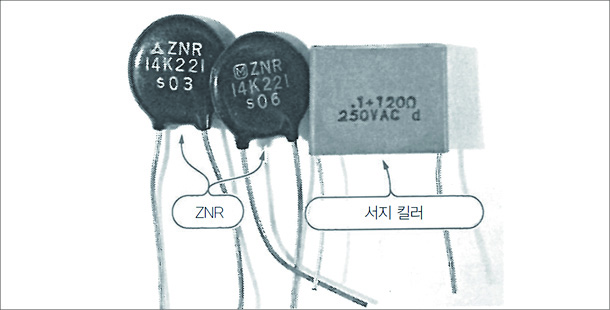

필름 콘덴서는 안정적인 용량값이 요구되는 아날로그 회로나 고내압이 필요한 전원회로 등에 많이 사용되고 있다. 다른 콘덴서에 비하면 내열성이 낮으므로 실장 시의 땜납 온도관리가 중요하다.

2. 적층 세라믹 콘덴서의 종류

(1) 분류와 용도

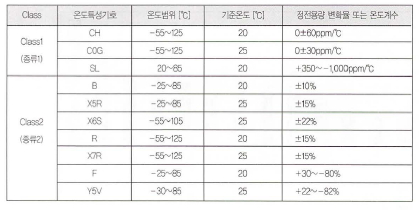

적층 세라믹 콘덴서에 다양한 종류가 있지만 특성적으로는 크게 Class 1과 Class 2의 2종류로 나뉜다.

세라믹 콘덴서는 세라믹의 배합비에 의해 온도 특성이나 용량 취득범위가 바뀌기 때문에 Class 1이나 Class 2의 규격이 존재한다. 표 1에 각 종류마다의 온도 특성 규격을 나타낸다.(3)(4)

▲ 표 1. JIS/EIA 규격에 의한 세라믹 콘덴서의 분류

Class 1의 콘덴서는 온도보상용 콘덴서라고 불리며 정전용량의 온도에 의한 변화가 비교적 직선적이고 또 손실도 작다는 특징이 있다.

용량범위는 1pF 이하의 미소용량 영역에서 1㎌ 전후의 고용량 영역까지 있으므로 모든 용도에 사용된다. 특히 100㎌ 이하의 미소용량 제품은 고주파회로에서의 매칭이나 커플링 용도에 사용된다.

Class 2의 콘덴서는 강유전체인 티탄산 바륨(BaTiO3)을 주원료로 한 고유전율의 유전체를 사용하고 있다. Class 1의 콘덴서에 비해 정전용량의 온도변화가 크고 손실도 커지지만 100㎌까지의 대용량을 얻을 수 있으므로 커플링 회로나 디커플링 회로, 평활회로 등에서 많이 사용된다.

전해 콘덴서에는 이러한 온도 특성에 의한 구별이 없고 규격화도 되어 있지 않다. 전해 콘덴서의 온도 특성은 유전체층인 탄탈 산화피막이나 알루미늄 산화피막의 온도 특성에서 결정돼버리기 때문이다.

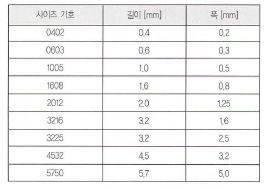

(2) 사이즈

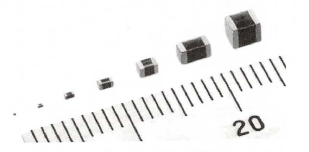

세라믹 콘덴서의 메이커, 실장기 메이커 및 세트 메이커간의 타협 하에 적층 세라믹 콘덴서의 사이즈가 표준화되었다. 사이즈의 표준화에 의해 기판 어셈블리 시의 실장효율 향상도 적층 세라믹 콘덴서 보급의 한 요인이 되었다. 표준 사이즈를 표 2에, 각 사이즈별 사진 1에 나타낸다.

▲ 표 2. 적층 세라믹 콘덴서의 사이즈 기호

▲ 사진 1. 적층 세라믹 콘덴서의 사이즈 비교 (왼쪽부터 0402, 0603, 1005, 1608, 2012, 3216, 3225 사이즈)

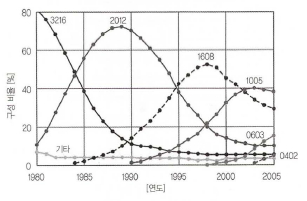

각 사이즈별 구성비율의 연도별 추이를 그래프로 나타낸 것이 그림 4이다. 1990년대 전반까지는 2012 사이즈가 가장 많이 사용 되었고 그 이후에는 1608 사이즈가, 최근에는 더욱 소형화된 1005 사이즈가 많이 사용되고 있다. 또 초소형 0603 사이즈, 0402 사이즈도 상품화되어 소형화가 급속히 진행되고 있다는 것을 간파할 수 있다.

▲ 그림 4. 적층 세라믹 콘덴서 사이즈의 동향

3. 적층 세라믹 콘덴서의 전기적 특성

적층 세라믹 콘덴서의 대표적인 특성항목에 관하여 간단히 해설한다.

(1) 절연저항(IR : Insulation Resistance)

이상적인 콘덴서라면, 콘덴서에 충전이 완료된 다음에는 유입하는 전류가 제로이지만 실제 콘덴서에서는 약간의 전류가 계속 흐른다. 이 전류를 누설전류라 한다. 세라믹 콘덴서인 경우, 이 누설전류는 전해 콘덴서에 비해 매우 작기 때문에 인가전압을 누설전류값으로 나눈 절연저항값으로 나타낸다. 절연저항값이 클수록 이상적인 콘덴서에 가까워진다.

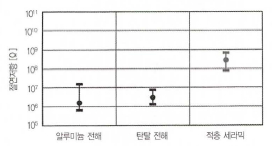

그림 5에 각종 콘덴서의 절연저항값을 나타낸다. 적층 세라믹 콘덴서는 전해 콘덴서에 비해 절연저항값이 2자리 정도 높다는 것을 알 수 있다. 따라서 대기 시 콘덴서의 누설전류가 걱정되는 용도에서는 적층 세라믹 콘덴서를 사용하는 쪽이 효과적이다. 또 전해 콘덴서에는 극성이 있으므로 역전압이 인가되면 절연저항값이 극단적으로 낮아진다. 적층 세라믹 콘덴서에는 극성이 없기 때문에 커플링 회로 등에서 콘덴서에 인가되는 전압이 반전되는 경우에도 걱정 없이 사용할 수 있다. 또 극성을 잘못 실장하여 발생하는 상태불량도 없다.

▲ 그림 5. 각종 콘덴서의 절연저항값 비교 (10㎌/15V)

(2) 절연파괴 전압(BDV : Break Down Voltage)

콘덴서에 전압을 인가하여 서서히 상승시켜 가면 어떤 전압에서 절연파괴가 일어난다. 이 전압을 절연파괴 전압이라 하며 직류, 교류, 펄스 등 인가하는 전압의 종류에 따라 값은 다르지만 콘덴서의 신뢰성을 나타내는 지표 중 하나이다. 또 세라믹 콘덴서나 전해 콘덴서인 경우, 파괴 모드는 쇼트로 되기 쉬우므로 세트에 내장된 상태에서 파괴되면 세트 전체가 파괴되는 경우도 있다.

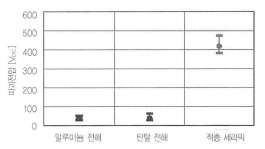

그림 6은 정격전압이 16V인 각종 콘덴서의 직류 파괴전압을 비교한 것이다. 정격전압은 같아도 콘덴서의 종류에 따라 파괴값은 크게 달라진다. 적층 세라믹 콘덴서는 전해 콘덴서에 비해 직류 파괴전압이 높기 때문에 서지나 펄스의 이상 전압에 의한 콘덴서의 절연파괴는 잘 일어나지 않는다. 그러나 세트 설계에 있어서는 정격전압을 초과하는 이상한 전압이 콘덴서에 인가되지 않도록 주의해야 한다.

▲ 그림 6. 10㎌/16V 각종 콘덴서의 직류파괴전압값 비교

(3) 온도 특성

콘덴서 중에는 온도를 변화시킬 경우 정전용량이 변화되는 것이 있다. 여기서 정전용량변화율 kTC는 다음과 같은 식으로 나타난다. 정전용량 변화율의 온도에 대한 특성을 온도 특성이라 부른다.

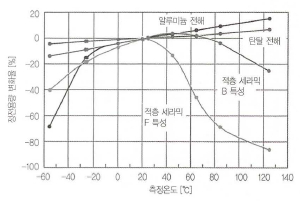

여기서, T : 측정 시의 환경온도 [℃], CT : T℃에서의 정전용량값 [F], C20:20℃(기준온도)에서의 정전용량값 [F] Class 2의 적층 세라믹 콘덴서 및 전해 콘덴서의 온도 특성을 그림 7에 나타낸다.

▲ 그림 7. Class2 적층 세라믹 콘덴서와 전해 콘덴서의 온도 특성 비교 (100㎌)

Class 2의 세라믹 콘덴서는 일반적으로 정전용량의 온도변화율이 곡선적이다.

대표적인 특성으로, 상온부근의 취득용량이 최대가 되도록 설계된 F 특성이 있다. 저온이나 고온 영역에서는 용량값이 크게 저하된다는 특징이 있지만 상온부근에서는 정전용량 체적비가 높은 콘덴서를 만들 수 있다.

한편, 저온에서 고온까지 작은 변화율로 안정적인 용량값을 유지하는 설계의 B 특성이 있다. 이러한 온도 특성은 세라믹 유전체의 주원료가 되는 티탄산 바륨에 각종 첨가물을 더함으로써 조정할 수 있다.

전해 콘덴서의 정전용량변화는 오른쪽으로 상상해가는 직선을 그리고 있으며 그 변화율은 세라믹 B특성(-25~85℃에서 ±10%)과 거의 같은 레벨이다.

그러나 습식 알루미늄 전해 콘덴서는 저온으로 될 경우, 음극측에 사용되고 있는 전해액의 이온 전도성이 저하되기 때문에 용량값이 대폭 저하된다.

(4) 직류 전압 특성(DC 바이어스)

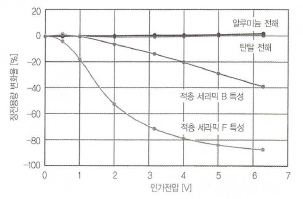

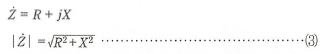

Class 2 세라믹 콘덴서의 특징적인 특성으로, 정전용량의 직류 전압의존성이 있다. 일반적으로 직류 전압 특성이나 DC 바이어스 특성이라 한다.

그림 8은 정전용량 100㎌, 정격전압 6.3V인 각종 콘덴서의 DC 바이어스 특성을 나타낸 것이다. 전해 콘덴서는 용량변화가 거의 없는데 대해 Class 2의 적층 세라믹 콘덴서는 직류전압의 증가와 함께 정전용량이 저하돼 간다. 따라서 정전용량을 중시하는 회로인 경우, Class 2의 세라믹 콘덴서는 DC 바이어스를 고려하여 설계해야 한다.

▲ 그림 8. Class2 적층 세라믹 콘덴서와 전해 콘덴서의 DC 바이어스 특성 비교 (100㎌/6.3V)

정전용량의 변화는 유전체층의 차이가 원인이다. 전해 콘덴서는 상유전체를 사용하고 있지만 Class 2의 적층 세라믹 콘덴서는 티탄산 바륨과 같은 강유전체를 사용한다.

강유전체에는 자발분극이 존재하고 DC 바이어스 특성은 자발분극의 크기에 따라 결정된다. 자발분극의 크기는 세라믹의 배합비에 의해 결정되므로 같은 Class 2의 세라믹 콘덴서라도 DC 바이어스 특성의 변화량은 다르다.

Class 1의 세라믹 콘덴서나 전해 콘덴서는 상유전체이므로 자발분극이 없다. 때문에 DC 바이어스 특성의 변화량은 매우 작은 값이다.

(5) 주파수 특성

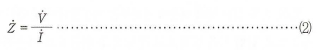

교류전압, 교류전류를 복소전압  , 복소전류

, 복소전류  라 생각했을 때 복소 임피던스

라 생각했을 때 복소 임피던스  는 다음과 같은 식으로 표현된다.

는 다음과 같은 식으로 표현된다.

또 복소 임피던스  는 실수성분과 허수성분으로 분류되므로 다음과 같은 식으로 표현된다.

는 실수성분과 허수성분으로 분류되므로 다음과 같은 식으로 표현된다.

이하, 복소 임피던스의 |  |를 임피던스라 부른다.

|를 임피던스라 부른다.

이상적인 콘덴서의 임피던스는 주파수와 함께 감소돼가지만, 실제 콘덴서는 어떤 주파수에서 상승하기 시작한다. 또 현실에서의 콘덴서는 종류에 따라 크게 다른 곡선을 그린다. 콘덴서의 주파수 특성은 중요하므로 여기서 상세히 설명한다.

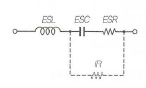

콘덴서는 콘덴서로서 동작하는 성분(ESC : Equivalent Series Capacitance) 외에 유전체나 전극의 손실 저항성분(ESR : Equivalent Series Resistance), 전극이나 리드선 등에 의해 발생하는 인덕턴스 성분(ESL : Equivalent Series Inductance), 그리고 유전체의 고체저항이나 표면저항이 있으며 등가회로는 그림 9와 같다.

▲ 그림 9. 콘덴서의 등가회로

여기서 절연저항의 값은 일반적으로 다른 소자성분의 임피던스값에 비해 충분히 크기 때문에 교류회로에서는 생략해도 된다. 이 때의 임피던스는 다음과 같다.

여기서, j : 허수단위, f : 주파수 [㎐]

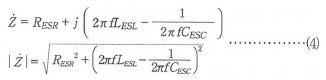

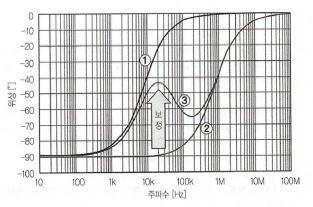

각 소자의 영향은 주파수 특성에 나타낸다. 그림 10과 같이 저주파 측에서는 ESC 성분에 따라 주파수에 반비례하여 임피던스가 저하돼 가는데, 어떤 주파수에서 임피던스값이 최소로 되는 점이 있다.

▲ 그림 10. 콘덴서의 임피던스-주파수 특성은 이러한 형태이다

이와 같이 최소로 되는 임피던스값은 콘덴서의 ESR에 의해 결정되고 소자로서는 저항과 같은 동작을 실행한다. 또 임피던스가 최소로 되는 주파수를 콘덴서의 자기 공진주파수라 부른다. 주파수를 올려 가면 ESL 성분의 영향이 강해지고 주파수에 비례하여 임피던스 값이 상승한다. 이 영역에서 소자는 인덕턴스로서 동작한다.

즉, 콘덴서가 콘덴서로서 동작하는 주파수영역은 공진주파수 이하의 저주파영역 뿐이라 할 수 있다.

여기서 ESR이 크면 자기 공진점 부근의 임피던스가 밀려 올라가 저항으로서 밖에 동작하지 않는 영역이 증가하고 콘덴서로서 기능하는 주파수영역이 감소돼버린다.

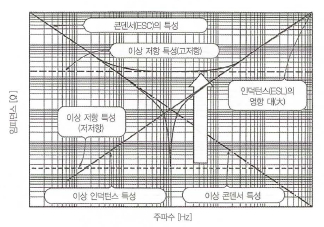

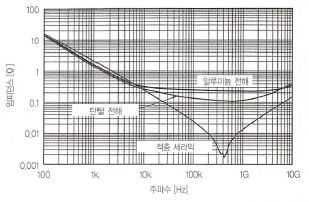

그림 11은 적층 세라믹 콘덴서와 각종 전해 콘덴서의 임피던스-주파수 특성이다.

▲ 그림 11. Class2 적층 세라믹 콘덴서와 전해 콘덴서의 주파수 특성 비교 (100㎌/6.3V)

적층 세라믹 콘덴서는 ESR과 ESL이 작기 때문에 전해 콘덴서에 비하면 고주파까지 임피던스가 낮아 우수한 주파수 특성을 나타낸다.

때문에 전원 라인에 사용하는 디커플링 콘덴서에 적층 세라믹 콘덴서를 사용했을 경우, 전해 콘덴서의 1/2~1/10의 정전용량값에서도 동등 이상의 노이즈 흡수효과가 얻어진다.

또 ESR이나 ESL이 작다는 것은 전원의 리플 노이즈 저감에도 효과가 있어 DC-DC 컨버터의 1차 측 평활 콘덴서나 2차 측 평활 콘덴서로서도 적층 세라믹 콘덴서를 사용하게 되었다.

(6) 발열 특성

콘덴서에 고주파 전류가 흐르면 다음 식과 같이 ESR에 비례하는 전력손실을 일으켜 발열한다.

Pe = I2 RESR ·············………………………………………………………··············(5)

여기서, Pe : 실효전력(소비전력) [W], I : 콘덴서에 흐르는 전류 [ARMS]

발열에 의해 콘덴서의 동작온도가 높아지면 콘덴서의 수명 단축으로 연결된다. ESR이 높은 콘덴서일수록 발열이 커져 많은 전류가 흐르지 않기 때문에 대전류가 흐르는 회로에는 ESR이 작은 콘덴서를 선택해야 한다.

그림 12에 각종 콘덴서의 리플 발열 특성을 나타낸다. ESR이 작은 콘덴서일수록 발열온도가 낮다는 것을 알 수 있다.

▲ 그림 12. 각종 콘덴서의 교류전류-발열 특성 (100㎌/6.3V, 100㎑)

적층 세라믹 콘덴서의 사용 방법

세라믹 콘덴서는 자기 콘덴서라고도 불리며 단단한 경화재로 만들어져 있다. 때문에 열적, 기계적 쇼크에 의해 균열되기 쉽고 적층 세라믹 콘덴서에서 발생하는 고장도 균열에 관한 것이 대부분이다.

특히, 기판 실장 시의 마운터(전자부품 자동장착기)에 의한 기계적 쇼크, 납땜 시의 열적 쇼크 및 납땜 후 취급 시의 기판 휨에 의한 응력에 주의해야 한다.

1. 사용상 주의점

(1) 기판설계상의 주의점

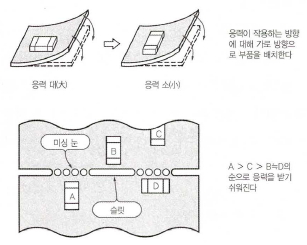

기판을 분할할 때, 커넥터를 접속할 때, 비스로 고정할 때 등, 콘덴서에 과도한 힘이 가해지는 경우가 있다. 그림 13은 부품배치의 위치와 기판분할 시 콘덴서에 가해지는 응력의 순서를 나타낸 것이다.

① 콘덴서를 분할위치에서 가급적 떨어뜨린다

② 기판의 휨에 콘덴서는 가로 방향으로 배치한다

③ 분할용 홈이나 슬릿을 설정한다.

등, 분할 시의 기판 휨을 억제할 수 있도록 연구하기 바란다.

▲ 그림 13. 부품배치와 기판분할 시의 응력

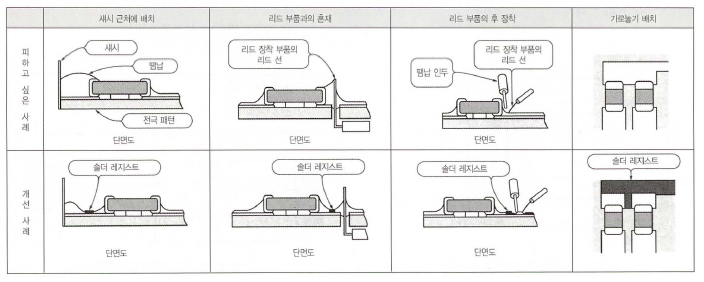

납땜 시의 땜납량이 과다해짐에 따른 열적, 기계적 쇼크를 받지 않도록 해야 한다. 솔더 레지스트를 사용하여 패턴 분할을 실행한 개선사례를 표 3에 나타낸다.

▲ 표 3. 솔더 레지스트를 사용하여 패턴 분할한 땜납 과다방지 개선사례

납땜 페이스트량이 과다해지지 않도록 레지스트 패턴 및 랜드 치수를 설계하기 바란다. 적절한 랜드 치수는 콘덴서메이커의 카탈로그를 참조하도록 한다.

(2) 마운터로 칩 장착 시 주의점

마운터 흡착 노즐의 하사점(下死点)이 너무 낮을 경우, 실장시 칩에 대해 과대한 힘이 걸려 칩 균열의 원인이 된다. 흡착 노즐 하사점은 기판의 휨을 교정하여 조정하기 바란다.

또 실장 시의 노즐 압력은 정(靜)하중에서 1~3N으로 하기 바란다.

흡착 노즐과 실린더 내벽 사이에 티끌, 먼지 등이 들어가면 노즐이 매끄럽게 움직이지 않고 실장 시 칩에 과대한 힘이 걸려 칩 균열의 원인이 된다.

클릭에 의해 위치결정을 실행하는 마운터에서 클릭이 마모되면 위치결정 시 칩에 가해지는 힘이 분산되어 칩 결함의 원인이 된다. 흡착 노즐의 하사점 조정, 위치결정 클릭의 보수/점검 및 교환은 정기적으로 시행하기 바란다.

(3) 납땜 고정 시의 주의점

세라믹 콘덴서는 무기재료를 사용하고 있으므로 유기재료를 사용하고 있는 콘덴서에 비해 내열성이 높다. 그러나 칩에 급격히 열을 가하면 내부에서 큰 온도차로 인한 변형이 발생, 균열의 원인이 된다.

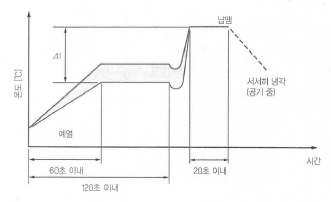

그림 14에 나타난 납땜온도, 납땜시간, 예열온도, 예열시간을 콘덴서 메이커의 지정범위 내로 되도록 온도 프로파일을 조정하기 바란다.

▲ 그림 14.리플로 납땜 시의 온도 프로파일

온도차 △T가 작아질수록 열적 쇼크도 작아지고, 칩 상승 및 변형 현상도 방지된다.

납땜 직후의 냉각과정은 급랭을 피하고 서서히 냉각시키기 바란다. 또 납땜을 반복하는 경우에는 누적시간이 규정된 범위 이하로 되도록 주의해야 한다.

리플로 납땜인 경우, 땜납 도포 두께가 너무 두꺼우면 납땜 페이스트량이 과다해져 열적 쇼크나 기판에서의 기계적 응력을 받기 쉬우므로 칩 균열의 원인이 된다. 땜납 도포 두께가 너무 얇으면 땜납의 고착력 부족이 발생, 칩 탈락이 원인이 된다. 땜납 도포 두께는 리플로 납땜 후 땜납이 잠기는 높이가 0.2mm 이상, 칩 두께 이하가 되도록 도포 두께의 분산을 억제하기 바란다.

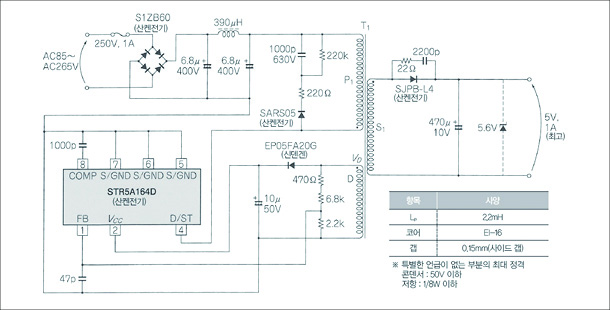

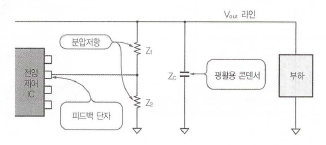

2. DC-DC 컨버터에서 출력전압이 이상 발진했다면

리니어 레귤레이터나 스위칭 레귤레이터에서 평활용으로 사용하고 있는 전해 콘덴서를 적층 세라믹 콘덴서로 치환했을 경우, 출력전압이 이상 발진을 일으키는 경우가 있다. 이것은 ESR이 큰 전해 콘덴서용으로 설계된 전원용 IC에서 ESR이 작은 적층 세라믹 콘덴서를 사용함으로써 일어나는 피드백 루프의 위상편차에 의한 것이다. 방지하는 방법으로는 다음과 같은 2가지 방법이 있다.

(1) 적층 세라믹 콘덴서 대응 전원용 IC로 교환한다

최근, 적층 세라믹 콘덴서의 특성에 맞춘 전원용 IC가 많은 IC 메이커에서 상품화되고 있다. 이러한 IC로 교환하는 것이 한 가지 방법이다.

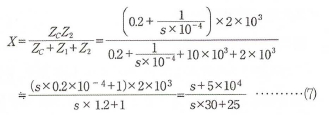

(2) 루프 위상을 보정할 수 있는 경우에는 위상의 편차를 조정해 본다

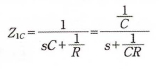

루프 위상은 전원용 IC의 피드백 전압 입력단자에서 조정한다. 이 입력부에 있는 분압저항을 조정하여 평활용 콘덴서부터 피드백 전압 입력단자까지의 전달함수 X의 제로점에서 맞춘다(그림 15).

▲ 그림 15. 전원용 IC의 피드백 단자 부근 회로

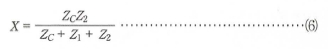

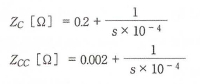

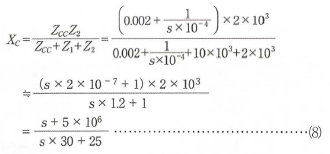

제로점이란, 분수함수의 분자를 제로로 하는 변수의 값을 말한다. 여기서는 라플라스 변환 s에 의해 주어지는 ZC(s)Z2(s)=0의 해가 된다.

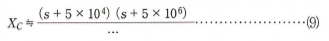

그렇다면 실제로 계산해보자. 그림 11의 알루미늄 전해 콘덴서 100㎌을 적층 세라믹 콘덴서 100㎌으로 치환했을 때 이상 발진했다고 가정한다. 치환되기 전의 값을 각각 Z1, Z2, ZC, 치환된 후의 ZC를 ZCC라고 하자.

콘덴서의 등가회로 모델은 그림 9를 사용하고 절연저항과 ESL은 무시한다. 그림 11에서 전에 콘덴서의 RESR은 0.2Ω 이므로,

로 된다. 여기서 분압저항을 Z1=10㏀, Z2=2㏀으로 한다.

식 (6)에 전해 콘덴서 사용 시의 각 소자 값을 대입하면,

으로 되며 제로점은 | s | =5x104으로 된다. 이 때 위상 특성은 그림 16의 ①과 같이 된다.

▲ 그림 16. 대책 후의 위상 특성곡선 변화 이미지

한편, 적층 세라믹 콘덴서로 치환되었을 때는,

으로 되며 제로점은 | s | =5x106으로 되고 위상 특성은 그림 16의 ②와 같이 엇갈린다.

콘덴서의 ESR이 2자리 작아지고 제로점이 2자리 커졌기 때문에 위상의 변화가 고주파 측으로 2자리 옮겨갔다. 이에 따라 피드백 루프의 위상이 -180° 에 근접, 여유가 없어져 발진을 일으키기 쉬워진다.

대책으로는 치환 후의 위상 특성을 초기상태로 근접시켜 실행하는 방법이 있다. 즉, 식 (8)을 식 (9)와 같이 하고 제로점을 새롭게 설정하면 된다.

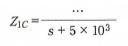

간단히 하기 위해 Z2를 고정하고 Z1을 조정하여 새롭게 제로점을 만든다. 이를 위해서는 Z1 을 Z1C로 변경하여,

으로 해주면 XC는 식 (9)와 같이 변형할 수 있다.

이 형태는 그림 17과 같이 Z1의 저항에 콘덴서 C를 병렬 접속함으로써 얻을 수 있다.즉,

로 된다. 이 때 분모끼리 비교하면,

으로 되어야 한다. 또 Z1C와 Z2의 직류에서의 분압비를 동일하게 하기 위해서는 R=Z1=10㏀이어야 하므로

으로 된다. 실제로 이 콘덴서를 설치한 위상 특성이 그림 16 ③의 특성이다. 다음에는 전원용 IC의 마진에 맞춰 소자를 조정하면 완성된다.

앞으로 전자기기는 고주파화와 함께 디지털화가 점점 진행될 것이라 생각된다. 이러한 용도에도 임피던스-주파수 특성이 우수한 적층 세라믹 콘덴서는 최적의 콘덴서로서 계속해서 사용될 것이다.

▲ 그림 17. 회로소자 변경

적층 세라믹 콘덴서의 대용량화에 대한 비밀

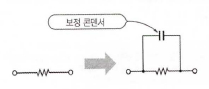

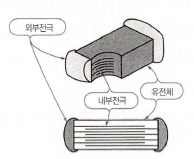

그림 18은 적층 세라믹 콘덴서의 적층구조 이미지이다. 유전체와 내부전극을 교대로 겹치고 각각의 내부전극은 외부전극과 교대로 접속하고 있다.

▲ 그림 18. 적층 세라믹 콘덴서의 적층구조 이미지

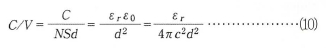

적층 세라믹 콘덴서의 단위 체적 당 정전용량 C/V/[F/㎣]는 다음과 같은 식으로 표현된다.

N : 유전체 적층 매수, S : 겹친 면적[㎟], d : 유전체층 두께[㎜], εr : 유전체 세라믹스의 비유전율, ε0 : 진공의 유전율, c : 진공 속의 광속 [m/s]

이 식에서 큰 값을 얻으려면 비유전율이 큰 재료에서 매우 얇은 유전체층을 형성해야 한다는 것을 알 수 있다. 특히 두께의 제곱에 반비례하여 C/V가 증가하므로 어디까지 박층으로 할 수 있는가가 큰 개발과제이다.

그림 19에 과거 10년 동안의 유전체 두께와 적층 매수의 변천을 나타낸다.

▲ 그림 19. 유전체 두께와 적층 수의 추이

1970년경 적층 세라믹 콘덴서의 유전체 두께는 100VDC 정격제품에서 40㎛, 50VDC 정격 제품에서 30㎛였다.(5) 그 후, 유전체 재료의 개량, 박막 시트 성형기술의 진보, 다층화기술의 진전에 의해 박층/다층화가 급속히 진행되었다. 특히 1990년 이후 엄청난 속도로 진보하여 1997년에는 3㎛, 2002년에는 1㎛의 박층 제품이 실용화되었다.

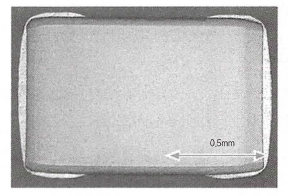

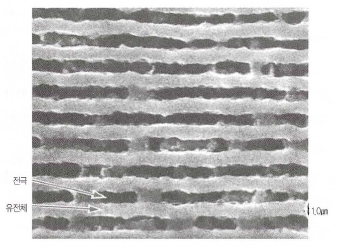

실제 콘덴서의 단면을 사진 2에 나타낸다. 중앙에 가득 채워진 곳이 전극층이지만 유전체의 두께는 1㎛밖에 되지 않으므로 겹쳐져 있는 모습은 육안으로 확인하기 힘들다. 그러나 전자현미경을 사용하면 사진 3과 같이 확인할 수 있다. 이러한 기술혁신에 의해 적층 세라믹 콘덴서는 정전용량의 확대 및 동일 용량값일 경우 더욱 소형화를 이룰 수 있게 되었다.

▲ 사진 2. 적층 세라믹 콘덴서의 단면

▲ 사진 3. 적층 세라믹 콘덴서의 단면도

유전체 두께 1㎛의 기술을 사용함으로써 20㎌/㎣를 초과하는 정전용량 체적비의 적층 세라믹 콘덴서가 생산되었고 탄탈전해 콘덴서와 같은 레벨에 도달하고 있다. 예를 들어 100㎌의 사이즈는 2000년에 5750사이즈(5.7x5.0㎜)였던 것이 2002년에는 4532사이즈(4.5x3.2㎜), 2003년에는 3225사이즈(3.2x2.5㎜)가 실용화되었고 2005년 중에는 3216사이즈(3.2x1.6㎜)가 실용화될 예정이다.

門 誠

本 記事는 日本 CQ出版社가 發行하는 「トラソジスタ技術」誌(2005年 4月號)와의 著作權 協定에 依據하여 提共받은 資料입니다.

게재월 | 2005 - 10  19050

19050  0

0