리니어 레귤레이터의 동작

출력 전압을 겨우 일정하게 유지하고 있는데, 식히고 싶다

리니어 레귤레이터(Liner Regulator)에 대해 설명한다. 리니어 레귤레이터는 시리즈 레귤레이터(Series Regulator) 라고도 한다.

1. 동작의 기본 … 저항으로 전압을 강하시켜 전원전압에서 원하는 전압을 얻는다

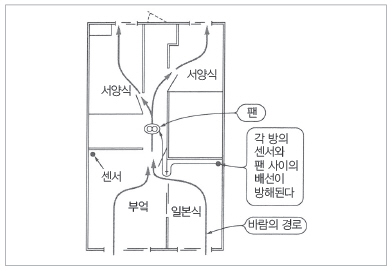

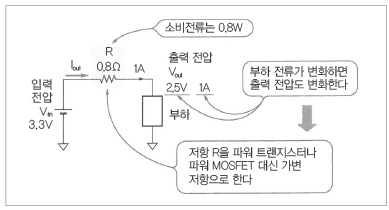

리니어 레귤레이터의 동작을 난폭하게 설명하면, 그림 1과 같이 입력 전압 Vin보다 낮은 DC 전압을 얻을 목적으로 저항 R을 회로 안에 넣어 강인하게 전압을 저하시킴으로써 원하는 전압을 얻는다.

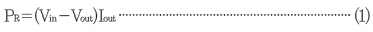

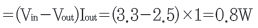

이 때, 저항 R에는 입력 전압 Vin- 출력 전압 Vout의 전압이 걸려 있다. 또한, 저항 R에는 전류 Iout이 흐르고 있다. 따라서 저항 R에는 다음과 같은 전력 손실이 발생한다.

전력 손실 PR은 저항을 따뜻하게 한다. 즉, 원하는 전압을 얻는 대가로 저항 R에서 전력 PR을 소비하는 것이다.

부하 전류에 변동이 없으면 그림 1과 같은 방법을 사용할 수 있을지도 모르지만, 유감스럽게도 전류 변동이 없는 부하는 탁상공론이며 현실에서는 있을 수 없다. 이것을 해결하기 위해서는 출력 전압이 일정해지도록 저항 R을 가변하면 될 것이다. 가변저항과 모터를 준비하고 출력 전압이 일정해지도록 가변저항을 돌리자… 라는 것은 물론 농담이다.

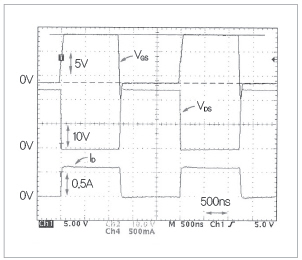

전자회로에서는 이 문제를 더 스마트하게 해결할 수 있다. 저항 R 대신 파워 트랜지스터나 파워 MOSFET(대전류 대응 타입 트랜지스터나 MOSFET)을 회로에 넣어 ON 저항을 가변시킴으로써 출력 전압을 일정하게 유지한다.

▲그림 1. 리니어 레귤레이터의 원리 (저항으로 전압을 강하시켜 원하는 전압을 얻는다.

부하 전류가 변하면 저항값이 자동적으로 변해 원하는 전압을 유지한다)

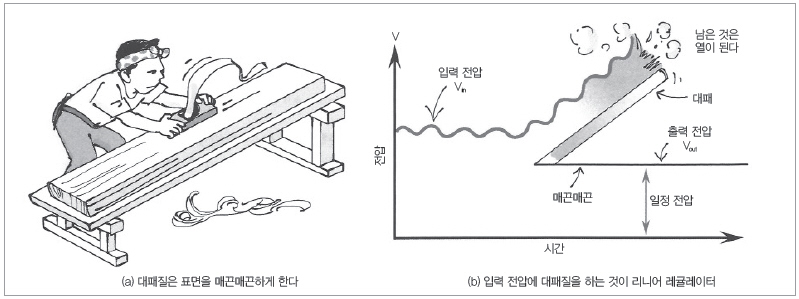

2. 리니어 레귤레이터는 대패

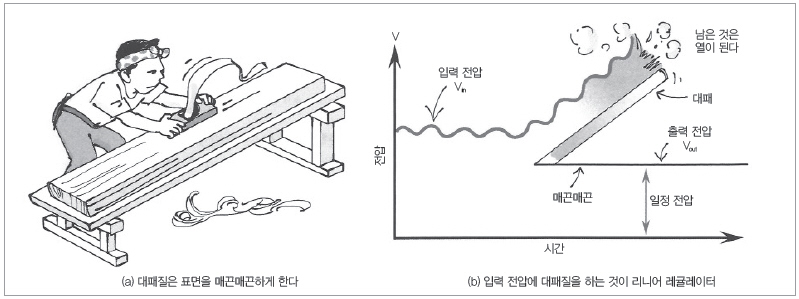

실제로 리니어 레귤레이터의 동작은 그림 2에 나타난 대패질과 같다. 그림 2(b)와 같이 여분의 입력 전압에 대패질을 실시하여 출력 전압이 될 때까지 깎아낸다. 그 결과 매끈매끈한 면, 즉 일정한 출력 전압을 얻을 수 있다.

▲그림 2. 대패질 이미지 (대패질을 하면 나무 표면은 매끈매끈해진다.

리니어 레귤레이터에 걸면 출력 전압값이 매끈매끈해진다)

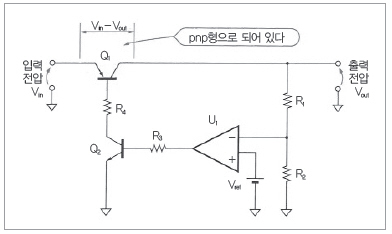

3. 기본 회로 … OP 앰프 전류 버퍼 회로

리니어 레귤레이터의 기본 회로는 그림 3(a)에 나타난 바와 같다. 트랜지스터 Q1의 컬렉터-이미터 전압은 항상 입력 전압 Vin-출력 전압 Vout이다. 이 전압 Vin-Vout이 대패로 깎는 전압이다. 가령 입력 전압 Vin이 높아졌다고 하자. 그 결과 대패로 깎은 전압 Vin-Vout이 커지고, 출력 전압 Vout은 일정하게 유지된다.

▲그림 3. 리니어 레귤레이터는 OP 앰프 전류 버퍼 회로 [회로도는 그리는 방법에 따라 감이 오거나 오지 않는다.

일반적으로 리니어 레귤레이터는 (a)가, OP 앰프 전류 버퍼 회로는 (b)가 많다]

그림 1의 저항 R을 예로 들어, 입력 전압 Vin이 높아지면 그만큼 트랜지스터 Q1의 ON 저항이 높아지도록 피드백이 작용한다. 그 결과 입력 전압 Vin-출력 전압 Vout이 커지고 출력 전압 Vout은 일정하게 유지된다.

여기서 그림 3(a)의 회로를 다시 그려 본 것이 그림 3(b)이다. 잘 살펴보면 그림 3(a)와 그림 3(b)는 같은 회로이다. 그림 3(b)의 회로는 OP 앰프 교과서에서 흔히 볼 수 있는 출력 전류를 증가시키는 회로로, 전류 버퍼 회로라고 한다. 즉, 리니어 레귤레이터는 OP 앰프 전류 버퍼 회로인 것이다.

그림 3(b)의 회로는 OP 앰프에 트랜지스터의 이미터 폴로어 회로가 추가되었다. 이미터 폴로어 회로이므로 트랜지스터 부분에는 전압 게인이 없다. 그렇게 되면 출력 전압 Vout은 OP 앰프의 비반전 앰프에 전압 Vref가 입력되었다고 간주할 수 있으므로 출력 전압은 식 (2)와 같이 나타낼 수 있다.

4. 출력 전압을 일정하게 하는 대가로, 깎아낸 전압이 열로 바뀐다

그런데 깎인 입력 전압의 일부는 어떻게 될까. 나무를 깎은 후 대패칩은 버려진다. 리니어 레귤레이터도 마찬가지로 재이용되는 경우는 없다. 깎인 전압은 입력 전압 Vin-출력 전압 Vout이다. 입력에서 출력으로 출력 전류 Iout이 흐르고 있으면, (입력 전압 Vin-출력 전압 Vout)×출력 전류 Iout의 전력이 트랜지스터 Q1에서 소비된다. 즉, 깎인 전압은 리니어 레귤레이터에서 열로 된다. 바꿔 말하면, 출력 전압 Vout이 일정해진 대가로 (Vin-Vout)Iout[W]의 전력이 열로 된 것이다.

5. 소비전력 1W 이하에서 사용하는 것이 현실적

열이 발생했다고 해서 리니어 레귤레이터에 대형 방열 팬을 달아 냉각하는 것은 현명하지 않다. 그 정도 크기의 전력을 다룰 경우, 나중에 설명하는 DC-DC 컨버터가 최적이다. 리니어 레귤레이터가 소비하는 전력은 5W 정도가 상한이며, 1W 이하에서 사용하면 방열 팬이 필요 없어지므로 현실적이다.

6. 소비전력을 낮게 억제하는 요령 … 입력 전압을 낮춘다

리니어 레귤레이터의 손실을 가능한 한 억제하려면 입력 전압 Vin을 가급적 낮게 하거나 출력 전류 Iout을 작게 하는 2가지 방법이 있다. 출력 전류 Iout은 부하 측 사정에 따라 결정되므로 입력 전압 Vin을 가급적 낮게 사용하자.

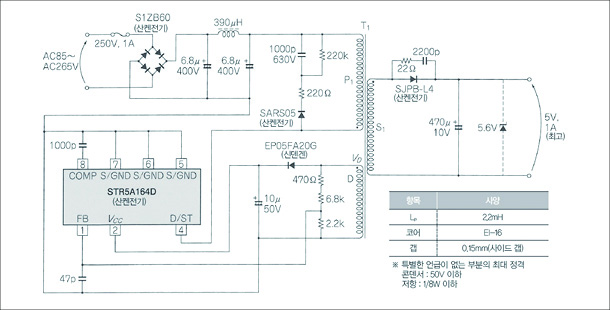

(1) 입력 전압에 하한값 ‘출력 전압+2.5V’가 있는 이유

그림 3의 회로에서 입력 전압 Vin을 점점 낮추면, 마침내 출력 전압 Vout도 일정하게 유지할 수 없게 된다. 즉, 출력 전압 Vout을 일정하게 유지하는 데에는 입력 전압 Vin-출력 전압 Vout에 하한 전압이 있다. 하한 전압은 회로 설계에 따라 다르지만 1.5V에서 2.5V 정도이다. 즉, 그림 3의 회로에서 입력 전압 Vin은 출력 전압 Vout+2.5V 정도 필요하다.

실제 그림 3의 회로에서는 트랜지스터 Q1의 컬렉터-이미터간 전압을 1V 이하로 하기가 어렵다. 그 이유는 트랜지스터 Q1의 베이스 전압 VB가 항상 출력 전압 Vout보다 베이스-이미터간 전압 VBE(≒0.6V)만큼 높아야 하기 때문이다. 즉, OP 앰프 U1의 출력 전압은 Vout+VBE 이상이어야 한다.

입력 전압 Vin이 내려가서 Vout+VBE ≧ Vin이 되면 어떠한 OP 앰프를 이용해도 Vout+VBE 이상의 출력 전압은 나오지 않으며, 이 시점에서 출력 전압 Vout이 내려가기 시작하는 것이다.

이 문제는 OP 앰프의 전원을 입력 전압 Vin에서가 아니라 입력 전압 Vin에서 3V 정도 높은 전압으로 하거나 별도의 전원으로 하면 개선할 수 있다.

발열을 억제하여 사용할 수 있는 저손실 타입의 리니어 레귤레이터

전원전압이 낮고 소비전류가 큰 CPU나 FPGA에 적합

1. 입력 전압을 거의 끝까지 낮춰도 동작한다

리니어 레귤레이터는 입력 전압 Vin을 낮추면 전력 손실이 작아지지만 그림 3에서의 입력 전압 Vin은 출력 전압 Vout+ 2.5V 정도가 하한이었다. 이 2.5V를 더 작게 하려는 노력이 이루어져 그림 4와 같이 저손실형이라고 불리는 회로 방식이 등장했다. 그림 4의 회로는 대전류를 제어하는 트랜지스터 Q1이 pnp형으로 되어 있는 것이 특징이다. 여기서 트랜지스터 Q1의 베이스 단자 전압은 입력 전압 Vin-베이스-이미터간 전압 VBE, 즉 Vin-VBE가 된다.

트랜지스터 Q1의 베이스 단자는 트랜지스터 Q2의 컬렉터와 저항 R4와 접속하므로 Q1의 베이스 전압은 0V 가까이까지 낮출 수 있다. 입력 전압 Vin이 내려가도 트랜지스터 Q1의 베이스 단자 전압 Vin-VBE를 0V 부근까지 낮출 수 있다.

최종적으로는 트랜지스터 Q1을 포화 영역까지 사용할 수 있다. 트랜지스터 Q1이 포화되면 컬렉터-이미터간 전압은 0.3V 정도의 전압이 된다. 트랜지스터 Q1이 포화되기 직전까지 컬렉터-이미터간 전압=입출력간 전압 Vin-Vout이 0.3V보다 약간 큰 0.5V 정도까지 출력 전압 Vout을 제어할 수 있다. 그림 4에 나타난 저손실형 리니어 레귤레이터의 입력 전압 Vin은 출력 전압 Vout+0.5V 정도까지 낮출 수 있다.

▲그림 4. 저손실 타입 리니어 레귤레이터의 기본 회로

2. 주요 용도 … CPU/FPGA용 전원

저손실형 리니어 레귤레이터가 특히 그 위력을 발휘하는 것은 CPU, FPGA 등의 코어용 전원으로 사용한 경우이다. 몇 가지 예를 들어 보자.

① 사례 1

주전원 3.3V에서 코어 전압 2.5V로 변환,

출력 전류 Iout=1A(출력 전력 2.5W)

저손실형 리니어 레귤레이터의 전력 손실

② 사례 2

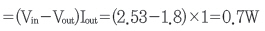

주전원 2.53V에서 코어 전압 1.8V로 변환,

출력 전류 Iout=1A(출력 전력 1.8W)

저손실형 리니어 레귤레이터의 전력 손실

3. 저손실 타입 사용 시 주의해야 할 점

(1) 입력 전압 Vin이 높을 때는 의미가 없다

전력 손실 관점에서 봤을 때, 저손실형 리니어 레귤레이터는 멋지다. 이것은 입력 전압 Vin이 낮아도 동작할 수 있기 때문이다. 만약 입출력간 전압 Vin-Vout이 3V 이상 걸어 사용하면, 일반적인 리니어 레귤레이터와 전력 손실이 같다.

(2) 안정도가 떨어진다

저손실형 리니어 레귤레이터는 일반적인 리니어 레귤레이터에 비해 안정도가 떨어진다. 이것은 저손실형 리니어 레귤레이터에서는 그림 4에 나타난 회로와 같이 트랜지스터 Q1의 컬렉터가 출력으로 되어 있기 때문이다. 결론부터 말하자면, 출력 측 커패시터 C2가 적층 세라믹 커패시터와 같은 저ESR 타입인 경우 불안정해지기 쉽다.

(3) 저소비전력화가 진행되는 최신 마이컴에는 필요 없다

CPU/FPGA용 전원에는 저손실형 리니어 레귤레이터라고 했지만, 반드시 그렇지 않은 경우도 있다.

현대의 CPU/FPGA는 전원전압이 저전압화되고 있다. 저전압화에는 확실히 저손실형 리니어 레귤레이터가 적합하다. 한편, CPU/FPGA 자체도 전력절감화 방향으로 나아가고 있다.

최신 CPU의 예를 들어 RL78/I1A(르네사스일렉트로닉스)로 실험해 보면, 16비트 CPU에서 곱합 연산 기능이 탑재되어 있음에도 불구하고 전원전류가 4.7mA였다. 이렇게까지 전원전압이 적으면 DC-DC 컨버터 등이 전혀 필요없다. CPU에 고분해능 A-D 컨버터를 탑재했으므로 저손실 타입이 아니라 출력 리플이 적은 일반적인 리니어 레귤레이터가 더 최적일 것이다. 기술 진보에 따라 선택하는 리니어 레귤레이터도 변하고 있다는 뜻이라고 생각된다.

다양한 리니어 레귤레이터 IC

기본 중의 기본! 3단자 레귤레이터에서 디스크리트의 저노이즈 회로까지

1. 이것이 기본! 3단자 레귤레이터 7805

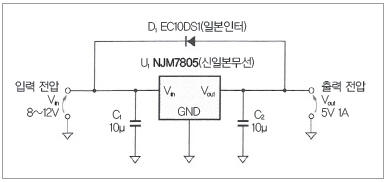

리니어 레귤레이터가 일렉트로닉스 분야에서 널리 유통되고 있는 것은 3단자 레귤레이터(그림 5)가 출현했기 때문이라고 생각된다. 3단자 레귤레이터의 내부는 그림 3, 그림 4와 등가이지만 그 이름대로 입력 전압 단자, 그라운드, 출력 전압 단자의 단자 3개밖에 없는 디바이스이다. 적은 부품과 편리성 때문에 3단자 레귤레이터를 사용하지 않는 전자기기를 찾는 것이 어려울 정도이다.

그림 5에 나타난 3단자 레귤레이터 NJM7805(신일본무선)는 기본 중의 기본으로, 정격 출력 전류 1.5A의 디바이스이다. 가격도 저렴하여 널리 사용되고 있다. 그림 5의 다이오드 D1은 입력 전압 Vin이 OFF되어 저감될 때, 내부 트랜지스터에 큰 역방향 전압(최악의 출력 전압 Vout과 같은 전압)이 가해지는 것을 방지한다. 범용적인 정류 다이오드를 사용할 수 있다.

(1) 기본이 되는 이유 ① … 다양한 출력 전압

모델명 7805는 +5V 출력을 나타내며, 그 외에는 7812가 +12V, 7815가 +15V 출력으로 되어 있다.

(2) 기본이 되는 이유 ② … 정격 전류도 다양

또한, 정격 전류도 0.5A 타입의 78M05, 0.1A 타입의 78L05로 시리즈화되어 있으며 종류도 풍부하다.

(3) 기본이 되는 이유 ③ … 다양한 반도체 회사에서 판매

동일한 모델명으로 각 반도체 회사에서 발매되고 있다.

(4) 기본이 되는 이유 ④ … 다양한 부전압 출력 타입

마이너스 전압 출력인 7905나 7805와 마찬가지로 시리즈화되어 있으며 이것도 종류가 풍부하다. 78** 시리즈와 비교하면 불안정하므로, 출력 측 커패시터의 커패시턴스는 메이커의 데이터시트를 참고하기 바란다.

그림 5. 기본 중의 기본! 5V 출력의 3단자 레귤레이터 7805

2. 78** 시리즈 외 … 소비전류가 신경쓰이는 용도에 사용

78** 시리즈의 문제점도 지적해 둔다. 이러한 78** 시리즈는 오래 전에 설계되었고 디바이스 내부의 소비전류가 다소 커 4mA 전후이다. 78L05는 내부 소비전류가 2mA나 된다. 그러므로 이 디바이스를, 10mA 이하로 출력 전류가 적은 용도에 사용할 경우 망설이게 된다.

78** 시리즈가 아닌 새로운 3단자 레귤레이터는 이 점까지 고려하여 자체 소비전류를 1/10 이하로 줄였다.

3. 사용자가 출력 전압을 설정할 수 있는 타입

출력 전압이 정해져 있을 경우 78** 시리즈의 3단자 레귤레이터에서 선정하면 충분하다. 하지만 출력 전압을 유저 측에서 설정하고자 할 때를 위해 조절할 수 있는 타입도 발매되고 있다.

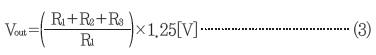

기본은 그림 6(a)에 나타난 317이다. 출력 전압 Vout은 그림 6(a)의 회로에서 식 (3)에 따라 설정할 수 있다.

317은 기본이지만 이것도 좀 오래 전에 설계되었다. 그래서 새로운 디바이스도 소개해 둔다. 그림 6(b)의 LT3080(리니어 테크놀로지)은 저항 1개로 출력 전압 Vout을 가변할 수 있으며 출력 전압 Vout[V]은 간단히 정할 수 있다.

또한, LT3080은 저손실형 리니어 레귤레이터이기도 하다.

그림 6. 이용자가 출력 전압을 설정할 수 있는 타입

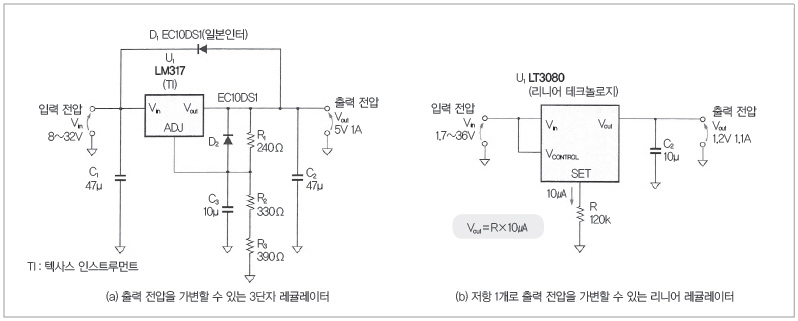

4. 저손실 타입 … 고정 전압형과 전압 가변형

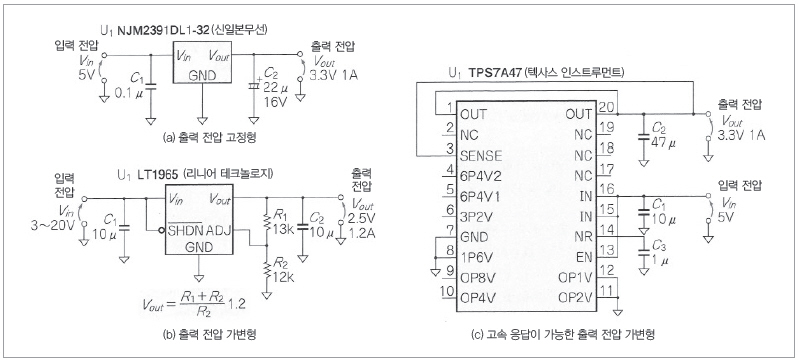

LDO(Low DropOut) 타입으로 불리는 저손실형 리니어 레귤레이터는 시대적인 요구 때문인지 최근 종류가 매우 많아지고 있다. 그림 7(a)는 가장 심플한 출력 전압 고정 타입이다. 그림과 같이 부품 수가 최소한으로 매우 적은 것도 특징이다.

그림 7(b)는 출력 전압 설정용 단자를 준비한 출력 전압 가변형 LDO이다. 2개의 외부 저항으로 출력 전압을 가감할 수 있다. 그림 7(c)는 고속 응답과 같이 LDO가 약한 분야를 극복한 새로운 디바이스이다. 출력 전압 가변형 LDO이지만 저항을 외장하지 않고 핀을 여러 개 준비하여 그 핀을 오픈으로 하거나, 그라운드에 접속하여 출력 전압을 선택하는 구조이다. 성능은 훌륭하지만 패키지가 QFN이므로 어느 정도 보급될지 앞으로 기대된다.

▲그림 7. 저손실 타입의 리니어 레귤레이터

5. 초저노이즈 회로 … 기준 전압의 노이즈 저감

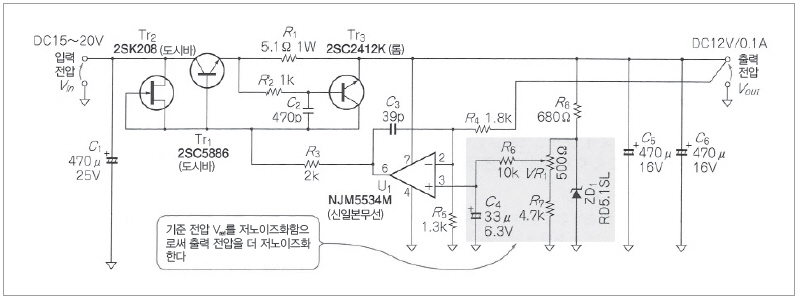

그림 8은 디스크리트 부품으로 구성한 리니어 레귤레이터이며 초저노이즈라는 것이 특징이다.

일반적으로 리니어 레귤레이터는 스위칭 방식 DC-DC 컨버터와 비교했을 때 압도적으로 낮은 노이즈이다. 그래도 리니어 레귤레이터로부터의 노이즈가 제로인 것은 아니다. 그 원인은 리니어 레귤레이터 IC 내부의 기준 전압 Vref에 있다. IC 내부의 기준 전압 Vref는 밴드갭으로 만들어져 있어, 약간이기는 하지만 밴드갭이 노이즈를 발생시킨다. 이 노이즈가 리니어 레귤레이터의 출력에 나타나는 것이다.

때문에 그림 8에서 기준 전압 Vref는 저노이즈 제너 다이오드로 만들고 그 출력을 저항 R6, 커패시터 C4의 LPF로 통과시킴으로써 노이즈를 차단하여 노이즈를 줄였다.

▲그림 8. 디스크리트로 만들면 가능한 저노이즈 전원 회로

![]()

本 記事는 日本 CQ出版社가 發行하는 「トランジスタ技術」誌와의 著作權 協定에 依據하여 提供받은 資料입니다.

게재월 | 2014 - 01  155701

155701  0

0